5月14日,国家科技体制改革和创新体系建设领导小组第十八次会议专题讨论了面向后摩尔时代的集成电路潜在颠覆性技术[1],引发了投资者对半导体行业潜在颠覆性技术的关注。

摘要

我们认为目前全球尤其是我国半导体产业正处于关键发展节点:1)摩尔定律接近物理极限,通过制程升级提高芯片性能越来越难;2)先进封装、化合物半导体等众多新技术近年来相继出现并快速发展;3)芯片缺货等因素使得全球各国意识到半导体产业供应链安全的重要性,相继出台政策支持本国半导体产业发展。

新型技术有望驱动后摩尔时代芯片性能进一步提升,我们梳理了集成电路潜在颠覆性技术。1)计算原理方面,量子计算、光子计算、类脑计算等技术使用量子作用法则、光子作用法则、类人脑信息处理法则替代经典电子计算与或非门表征计算,理论上可在部分类型算法上实现计算效率的大幅提升。2)材料、器件方面,第二/三/四代半导体(GaAs、GaN、SiC、Ga2O3等)具有宽禁带、高导热率、高抗辐射等优势,在高速、高频、大功率等应用场景相较第一代半导体(Si)具有显著优势,随着5G、新能源技术的发展,化合物半导体的应用正逐步提升。碳基器件(石墨烯、碳纳米管等)具有高电子迁移速率优势,理论上能够以比硅基器件高近200倍的速率工作。柔性器件(碳纳米管、ZnO等)理论上可以较好适配柔性电子领域应用。新型存储器(相变存储器、铁电存储器、磁性存储器、阻变存储器等)相较DRAM、NAND Flash、NOR Flash等传统存储器具有高可靠性、高读写速度、低功耗等优势,正逐步向市场推广。3)计算架构方面,RISC-V具有完全开源、架构简单、模块化设计等优势,目前正在物联网等领域积极推广,未来有望成为和x86、ARM比肩的重要架构之一。异构计算(CPU+GPU、CPU+FPGA、CPU+ASIC等)能够充分发挥不同计算平台的优势以提升计算效率(例如让CPU从事管理和调度,而将计算交给运算能力更强的GPU),随着AI技术的发展(尤其是CUDA等技术的出现),异构架构目前已经得到了较为广泛的应用。存算一体(阻变存储器等)将目前计算机存储和运算两大基本功能单元合二为一,理论上能够和AI算法(神经网络)形成较好耦合。4)芯片集成方面,Chiplet(芯粒技术)、SiP(系统级封装)、3D堆叠等先进封装技术能是封装产业未来重要发展趋势。此外,我们认为在半导体设备、材料、工艺,软件层面的算法、应用也存在出现颠覆性技术的可能性。

风险

半导体潜在颠覆性技术进展不及预期。

正文

部分潜在颠覆性技术简介

量子计算

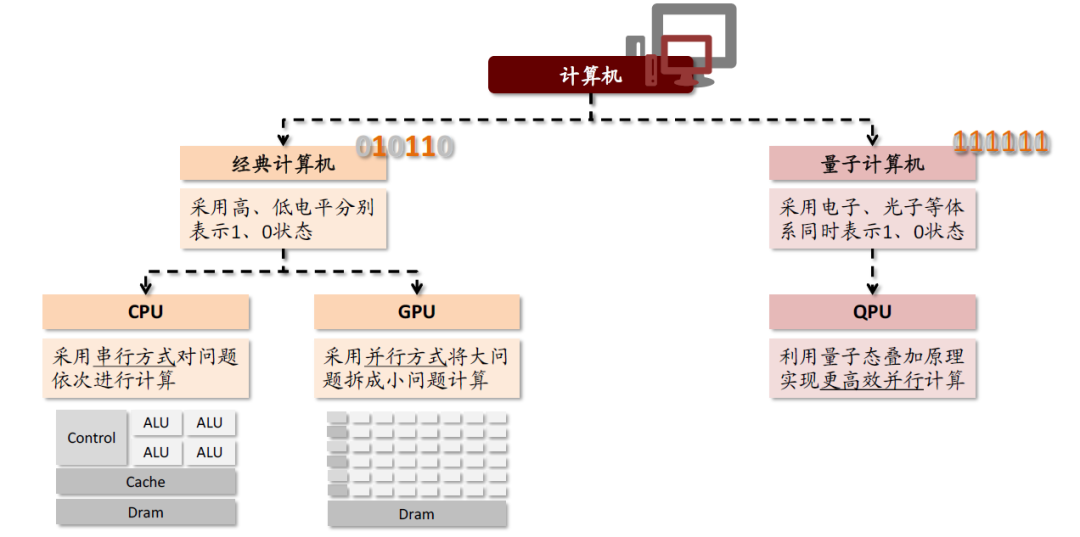

量子计算机是基于量子力学原理构建的计算机。量子态叠加原理使得量子计算机每个量子比特(qubit)能够同时表示二进制中的0和1,从而相较经典计算机算力发生爆发式增长,形成“量子优越性”。在解决实际问题的过程中,CPU采用“串行”计算,即将一个问题的若干部分按照顺序依次进行运算;GPU采用“并行”计算,即将一个问题拆成若干个小问题后,同时对每个小问题的一部分进行运算;QPU则利用量子叠加性快速遍历问题的各种可能性并找到正确答案。形象地说,CPU算力随比特数n的增长呈线性n增长,GPU算力随比特数n的增长呈平方次n×n增长,QPU算力随比特数n的增长呈幂指数2n增长。

图表:CPU、GPU、QPU概念及原理对比

资料来源:CSDN,中金公司研究部

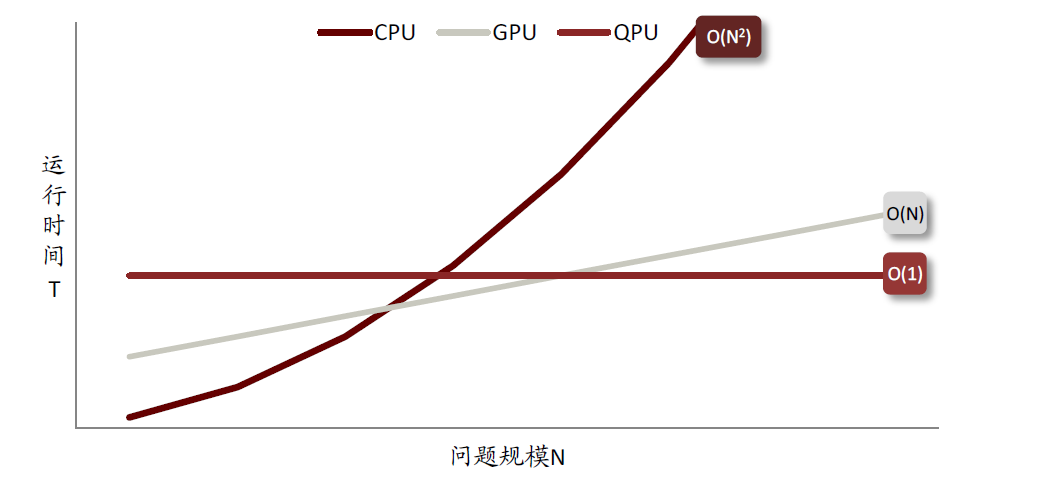

为具体说明量子计算机的高效性,我们假设存在一个同时适用CPU、GPU、QPU解决的问题。理想状态下,如果基于CPU开发的经典算法时间复杂度为O(N2),那么经过GPU并行计算优化后运行时间就会降为O(N),而基于QPU开发的全新量子算法时间复杂度仅为O(1)。实际运行中,CPU向GPU传输数据等操作需要消耗一定时间,QPU为获得运行结果的概率分布所做的多次观测也需要消耗一定时间。问题规模较小时CPU实际运行时间有可能较小,但是随着问题规模的增大,最终运行时间将呈CPU>GPU>QPU排列。

图表:CPU、GPU、QPU计算效率对比——针对CPU算法时间复杂度为O(N2)的问题

资料来源:CSDN,中金公司研究部

注:本图仅作概念性说明“量子优越性”

科学家预测,经典计算机未来仍将承担收发邮件、视频音乐、网络游戏等功能,而量子计算机则将用于解决大型分子模拟、寻找大数质因数等经典计算机无法模拟的领域,并在AI计算领域对传统算力进行提升。

先进封装

先进封装:FIWLP&FOWLP,PLP

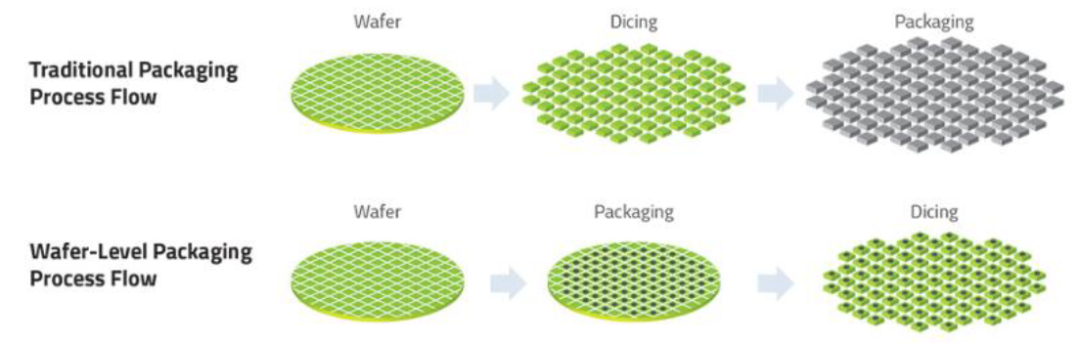

首先我们先要提及Wafer-level packaging (WLP,晶圆级封装)的概念。在传统封装概念中,晶圆是先被切割成小的晶粒,之后再进行连接和塑封。而晶圆级封装工序恰好相反,晶圆级封装将晶粒在被切割前封装完成,保护层将会被附着在晶圆的正面或是背面,电路连接在切割前已经完成。

图表:晶圆级封装示意图

资料来源:Semi Engineering,中金公司研究部

图表:晶圆级封装流程图

资料来源:Aptos Technology,中金公司研究部

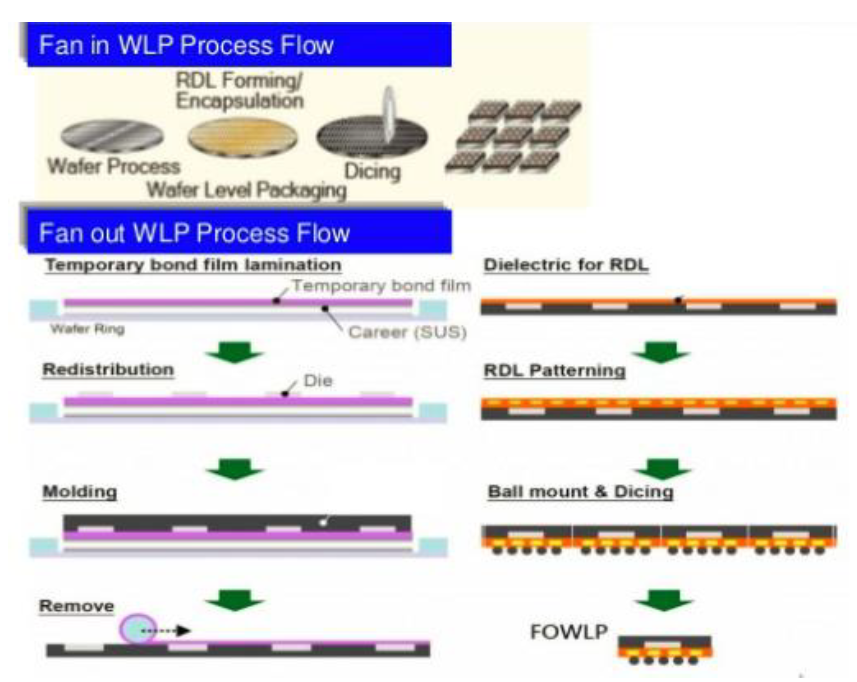

FIWLP:全称Fan-in Wafer-level packaging, 又称WLCSP(Wafer-level Chip Scale Package),扇入式晶圆级封装,也就是传统的晶圆级封装,切割晶粒在最后进行,适用于低引脚数的集成电路。随着集成电路信号输出的引脚数目的增加,焊锡球的尺寸也就变得越来越严格,PCB对集成电路封装后尺寸以及信号输出接脚位置的调整需求得不到满足,因此衍生出了扇出型晶圆级封装。扇入晶圆级封装的特征是封装尺寸与晶粒同大小。

FOWLP: 全称Fan-out Wafer-level packaging,扇出式晶圆级封装,开始就将晶粒切割,再重布在一块新的人工模塑晶圆上。它的优势在于减小了封装的厚度,增大了扇出(更多的I/O接口),获得了更优异的电学性质及更好的耐热表现。

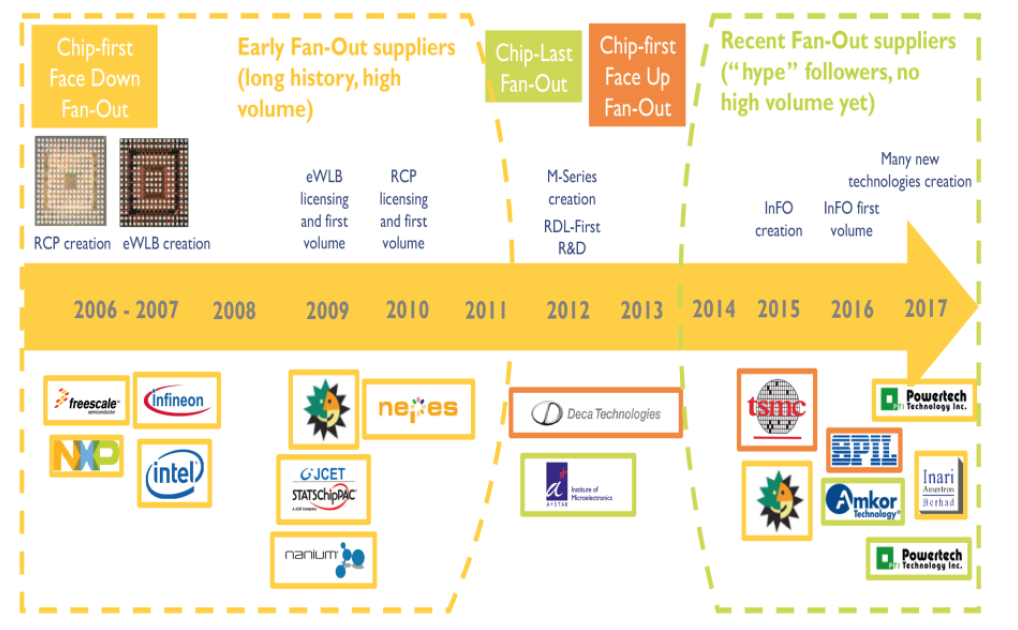

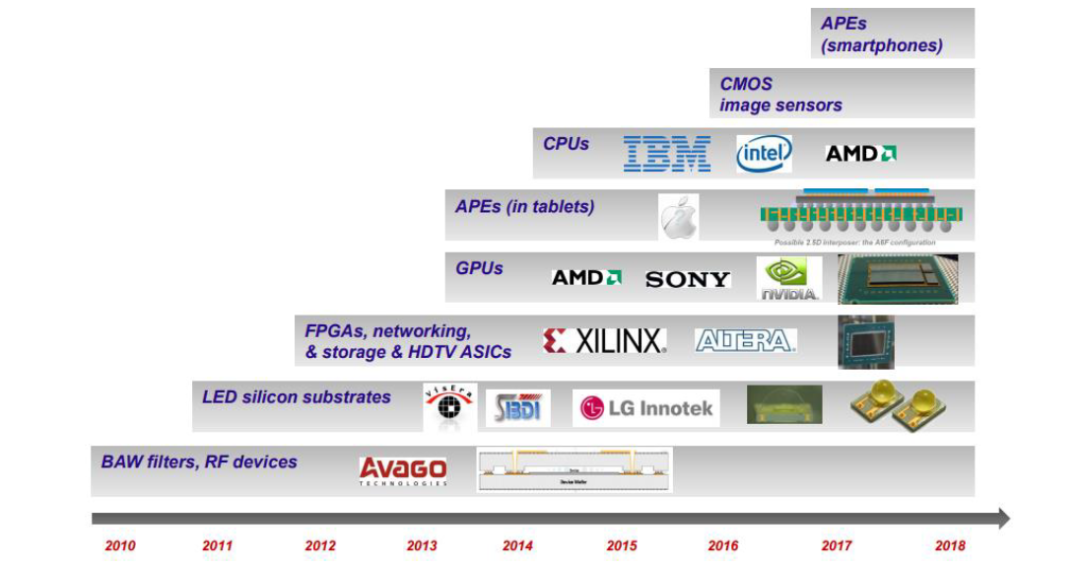

图表:扇出式封装发展历史

资料来源:Yole,中金公司研究部

FIWLP与FOWLP用途不同,均为今后的主流封装手段。FIWLP在模拟和混合信号芯片中用途最广,其次是无线互联,CMOS图像传感器也采用FIWLP技术封装。FOWLP将主要用于移动设备的处理器芯片中。

根据Yole的预测,2018年以前FOWLP的主要驱动为苹果智能手机的处理器芯片,2018年以后的FOWLP的主要驱动除了其他安卓手机处理器的增长,主要是高密度FOWLP在其他处理芯片的应用,如AI、机器学习、物联网等领域。

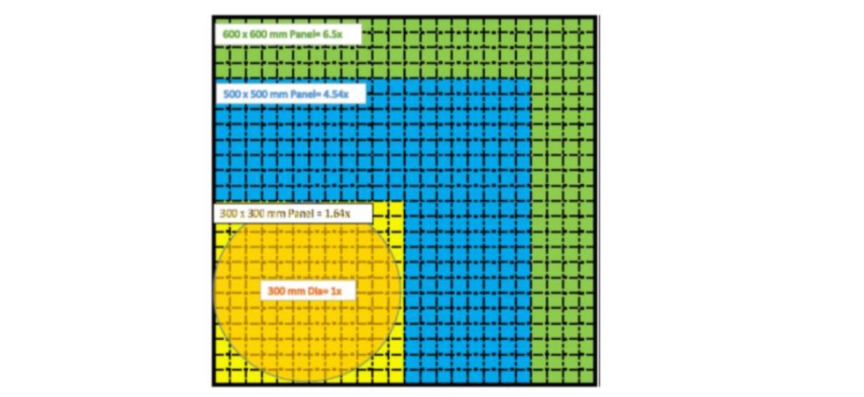

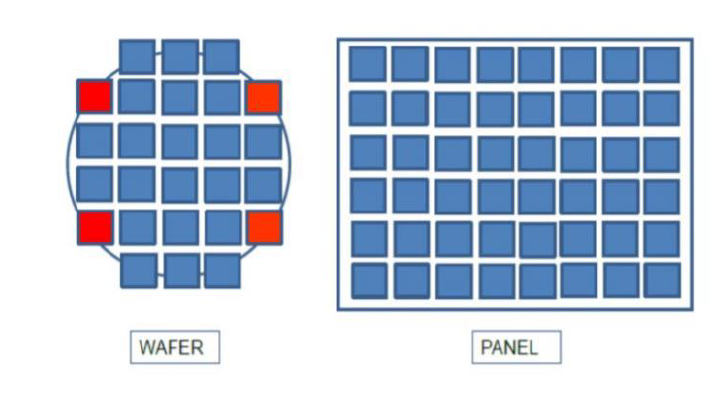

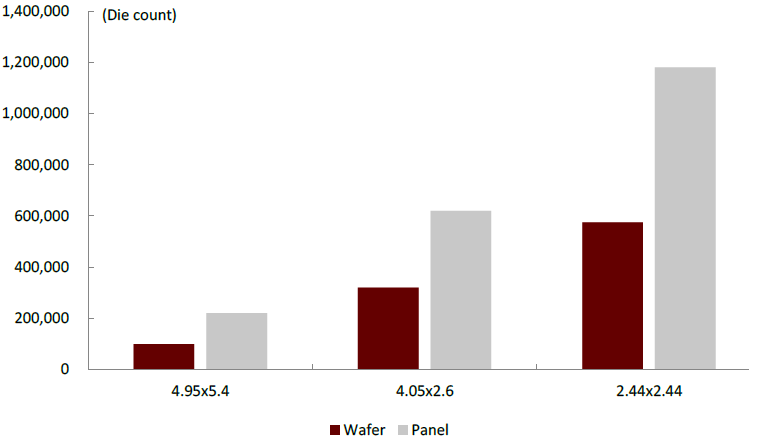

PLP:全称Panel-level packaging,平板级封装,封装方法与FOWLP类似,只不过将晶粒重组于更大的矩形面板上,而不是圆形的晶圆。更大的面积意味着节约更多的成本,更高的封装效率。而且切割的晶粒为方形,晶圆封装会导致边角面积的浪费,矩形面板恰恰解决了浪费问题。但也对光刻及对准提出了更高的要求。

图表:PLP与WLP的尺寸对比

资料来源:Semi Engineering,中金公司研究部

图表:矩形面板有效解决了面积浪费

资料来源:IEEE,中金公司研究部

图表:更大基板(600mm x 600mm)带来的效率提升

资料来源:IEEE,中金公司研究部

2.5D封装:RDL & 中介层

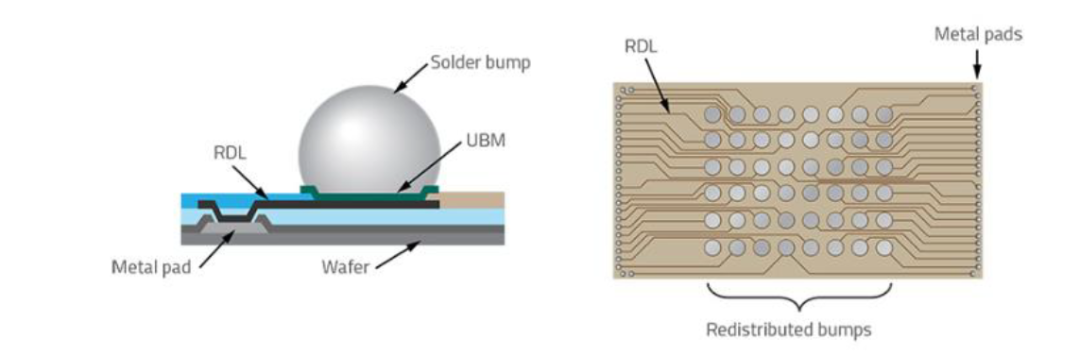

RDL(Redistribution layer,再分布层):在晶圆水平上,触点再分布可以很高效的进行。再分布层用于使连线路径重新规划,落到我们希望的区域,也可以获得更高的触点密度。再分布的过程,实际上是在原本的晶圆上又加了一层或几层。首先淀积的是一层电介质用于隔离,接着我们会使原本的触点裸露,再淀积新的金属层来实现重新布局布线。UBM在这里会被用到,作用是支撑焊锡球或者其他材料的接触球。

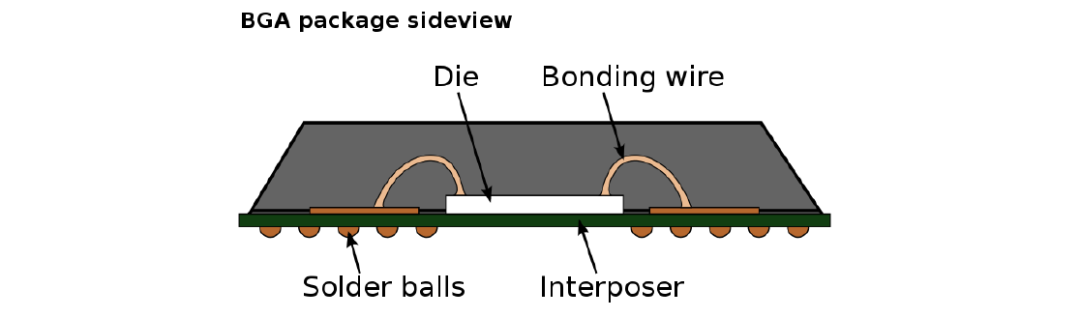

中介层(Interposer):指的是焊锡球和晶粒之间导电层。它的作用是扩大连接面,使一个连接改线到我们想要的地方。与再分布层作用类似。

图表:再分布层(RDL)示意

资料来源:Semi Engineering,中金公司研究部

注:此数据于2017年预测

图表:中间层(Interposer)示意

资料来源:Semi Engineering,中金公司研究部

图表:中间层(Interposer)技术发展路径

资料来源:Yole,中金公司研究部

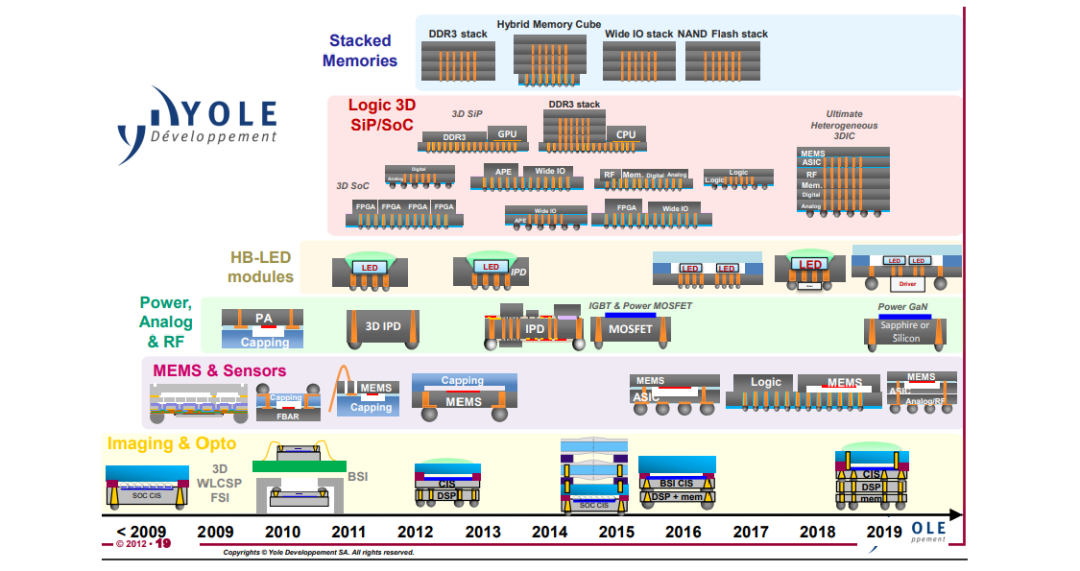

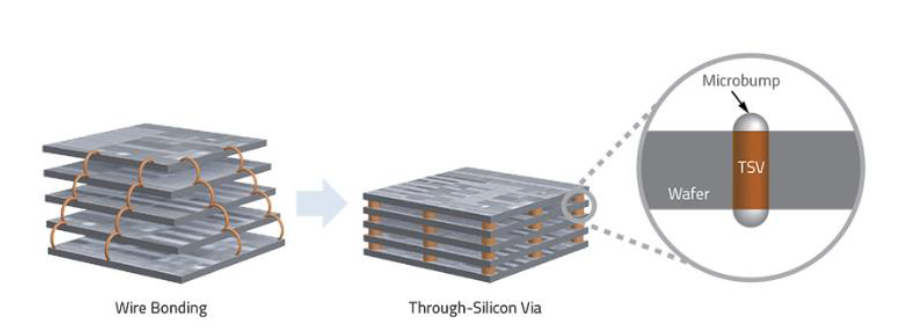

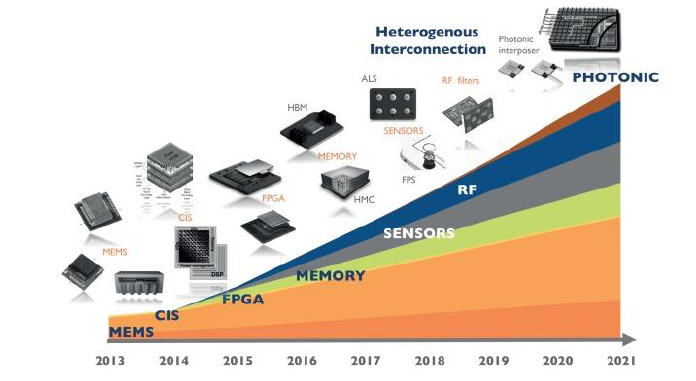

3D封装:TSV,PoP和MEMS

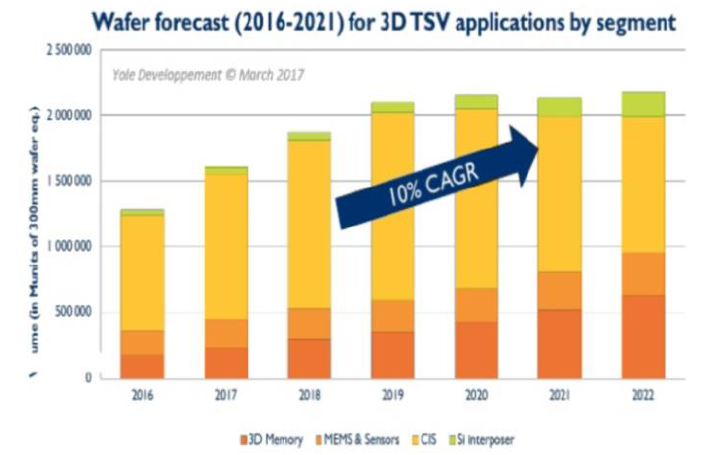

TSV(Through-silicon via,硅通孔):Bump和RDL会占用芯片接合到基板上的平面面积,TSV可以将芯片堆叠起来使三维空间被利用起来。更重要的是,堆叠技术改善了多芯片连接时的电学性质。引线键合可以被用于堆叠技术,但TSV吸引力更大。TSV实现了贯穿整个芯片厚度的电气连接,更开辟了芯片上下表面之间的最短通路。芯片之间连接的长度变短也意味着更低的功耗和更大的带宽。TSV技术最早在CMOS图像传感器中被应用,未来在FPGA、存储器、传感器等领域都将被应用。根据Yole预测,2016~2021年,应用TSV技术的晶圆数量将以10%的年复合增长率增长。3D存储芯片封装也会在将来大量的用到TSV。

图表:3D IC和TSV技术演进路径

资料来源:Yole,中金公司研究部

图表:TSV技术示意图

资料来源:Semi Engineering,中金公司研究部

图表:TSV技术发展路径

资料来源:Yole,中金公司研究部

图表:TSV市场规模

资料来源:Yole,中金公司研究部

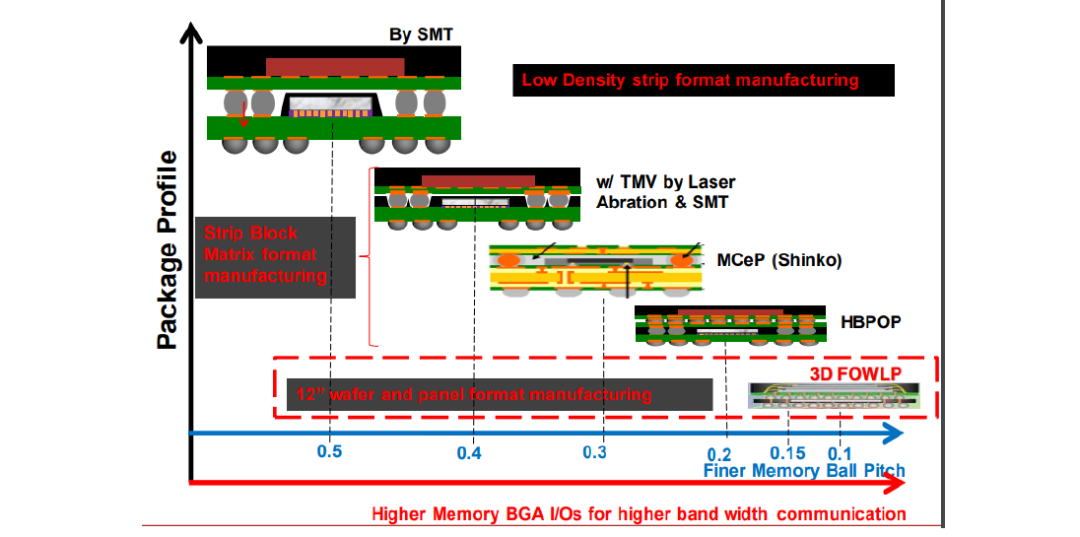

PoP(Package on Package,堆叠封装):PoP是一种将分离的逻辑和存储BGA(Ball grid array,球状引脚栅格阵列)包在垂直方向上结合起来的封装技术。在这种结构中,两层以上的封装单元自下而上堆叠在一起,中间留有介质层来传输信号。PoP技术增大了器件的集成密度,底层的封装单元直接与PCB板接触。传统的PoP是基于基板的堆叠,随着存储器对高带宽的需求,球间间隔要求更小,未来将会与FOWLP技术相结合,做基于芯片的堆叠。

图表:PoP技术演进趋势

资料来源:ASMPT,中金公司研究部

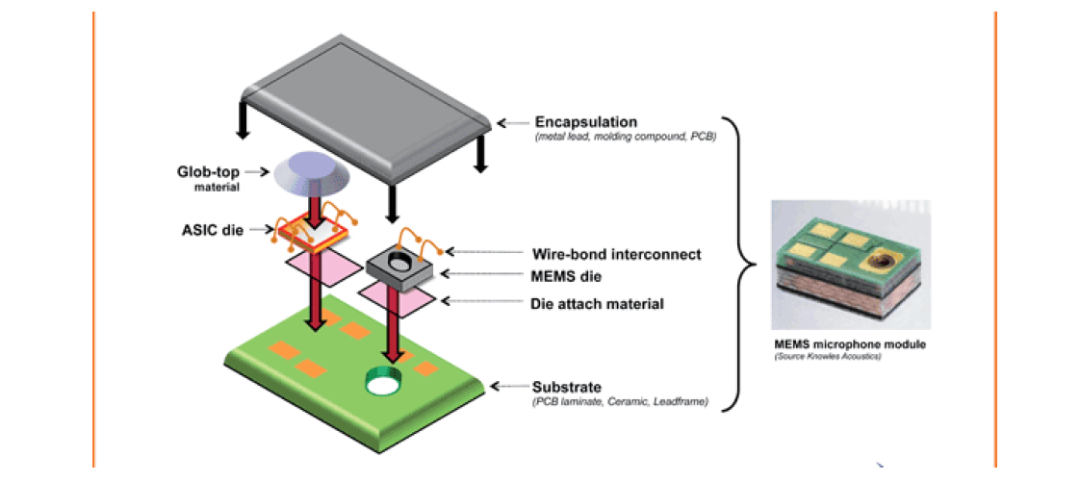

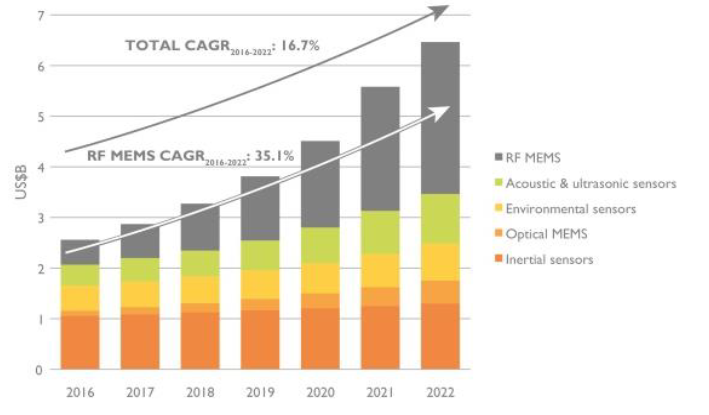

MEMS封装:微机电系统在近些年应用越来越广泛,随着传感器、物联网应用的大规模落地,MEMS封装也备受关注。MEMS的封装不同与集成电路封装,分为芯片级、模组级、卡级、板级、门级等多元垂直分级封装,设计时也需考虑不同模组间的相互影响。Yole测算2016年MEMS封装市场规模在27亿美元左右,Yole预计2016~2022年间市场规模将会维持16.7%的年复合增长率高速增长,其中RF MEMS封装市场是主要驱动,2016~2022年间,年复合增长率高达35.1%。

图表:MEMS封装技术示意图

资料来源:Yole,中金公司研究部

在整个MEMS生态系统中,MEMS封装发展迅速,晶圆级和3D集成越来越重要。主要的趋势是为低温晶圆键合等单芯片集成开发出与CMOS兼容的MEMS制造工艺。另一个新趋势是裸片叠层应用于低成本无铅半导体封装,这种技术可为量产带来更低的成本和更小的引脚封装。但是,MEMS器件的CMOS和3D集成给建模、测试和可靠性带来挑战。

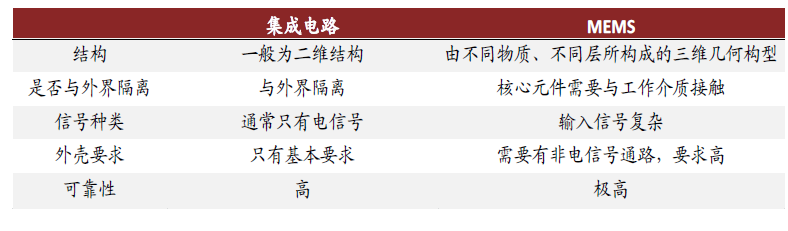

图表:MEMS 封装的特殊性

资料来源:中金公司研究部

图表:MEMS封装市场规模预测

资料来源:Yole,中金公司研究部

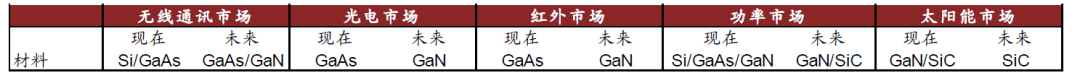

化合物半导体

图表:化合物半导体应用和材料之间的关系

资料来源:中金公司研究部

GaN在微波、电力电子以及光电领域的应用

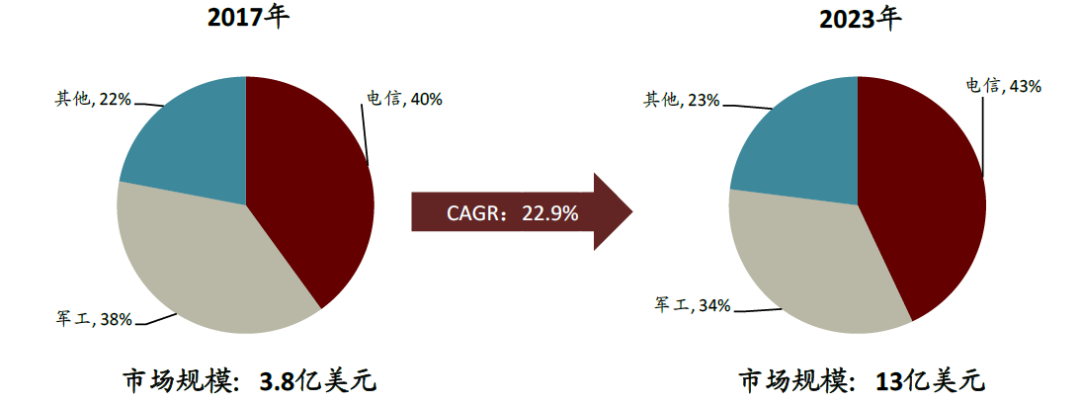

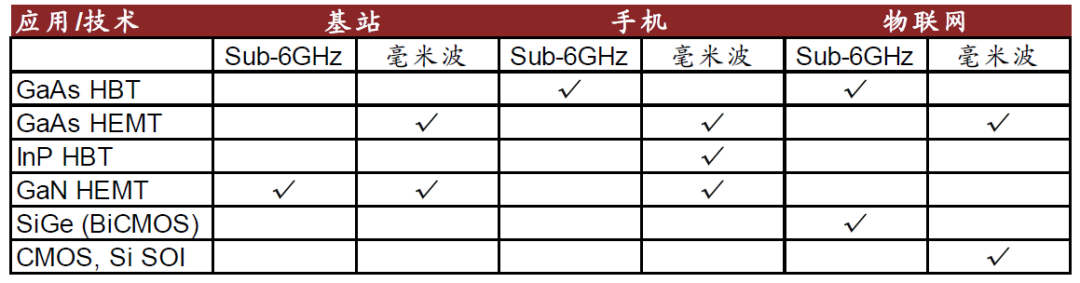

1)WaveTek认为,对于5G解决方案,需要功率放大器兼具高线性度和高效率的特性。由于传统的LDMOS器件在高频段、高带宽的应用效率不及第三代化合物半导体的GaN器件,随着未来工作频率进一步提高,GaN器件(<50V)的优势会进一步显现。目前GaAs和GaN能够满足完整的5G实施方案所需的高频性能。根据Yole测算,整体射频用GaN器件市场空间从2017年的3.8亿美元增长到2023年的13亿美元,CAGR 22.9%。其中最主要应用为电信部分,包括智能手机射频前端模组、基站等,第二大应用为军工,包括雷达、夜视仪等。

图表:2017-2023用于射频GaN器件市场容量CAGR将达到22.9%

资料来源:Yole,中金公司研究部

由于缺乏低成本的GaN衬底,目前主流的外延生长方式为GaN-on-SiC和GaN-on-Si.Qorvo目前的GaN器件都采用GaN-on-SiC的工艺,Qorvo认为SiC衬底外延出的GaN器件具有更高的可靠性以及更低的整体成本。

图表:高频性能的需求促使GaN器件在射频中渗透率增长,而对于物联网等追求低功耗、低成本的应用,则可使用CMOS工艺器件替代

资料来源:WaveTek,中金公司研究部

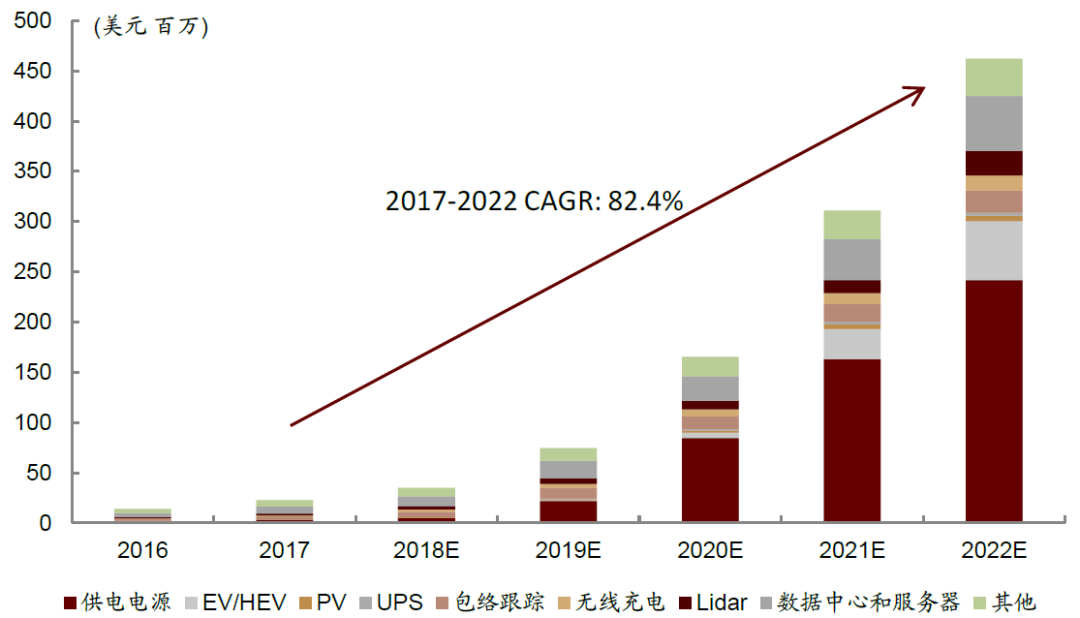

2)电力电子领域是GaN另一大应用市场,高压(650V)/低压(<200V)GaN功率器件能为AC-DC、DC-DC隔离电源、负载点电源功能带来附加值,因此在数据中心、通信、交流快速充电等领域发挥越来越重要的作用。根据Yole预测,GaN功率器件市场规模将从2017年的2,300万美元扩展到2022年的4.6亿美元,其中供电电源为最大应用,2022年占比达到52.3%。

图表:相较于射频市场,虽然电源市场的规模较小,但增速更快,2017-2022 CAGR达到82.4%

资料来源:Yole,中金公司研究部

注:此数据于2017年预测

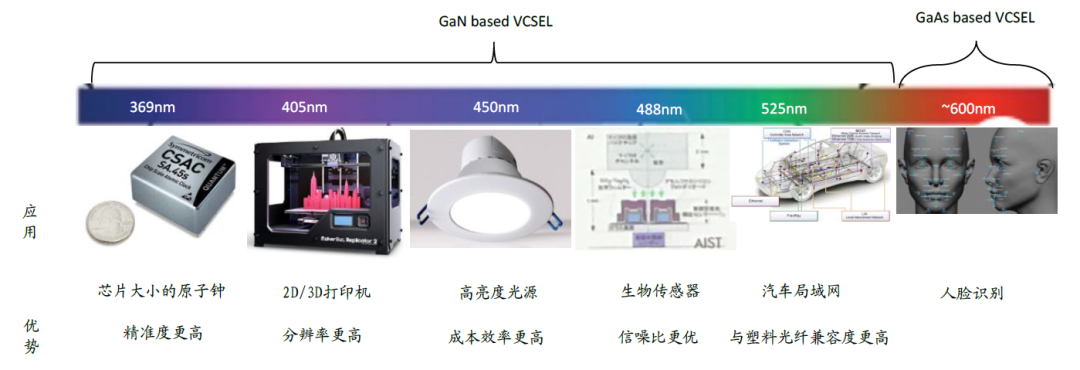

3)Sony认为,由于GaN材料能够拓展光谱至蓝绿光范围(369-525nm),因此能够进入某些新兴的应用领域并取得更好的效果。例如,在405nm波长下,GaN VCSEL能够取代GaAs VCSEL应用在2D/3D打印机中,由于蓝光的波长短于红光,因此可以实现更精细的分辨率;又例如在488nm波长下,GaN VCSEL能够使用在生物传感器中,可以扩大塑料光纤中光通信的效率,在红色和红外线中低成本的波导具有很高的光损失,但在绿色光线中不会发生。我们预计仅就智能手机用VCSEL市场规模2017年就已达到1亿美元左右,相信未来随着GaN器件的发展将有效增加VCSEL在各个应用领域的渗透率。

图表:由于GaN基VCSEL能够拓展光谱至蓝绿光,因此能扩展更多应用领域

资料来源:Sony,中金公司研究部

SiC:宽带隙功率器件首选材料

SiC在高温、高频、高压、热导率、衰减电场特性方面都表现良好,可以支持600伏以上甚至到2,000伏的电压,非常适用于宽带隙功率器件,因此可大量使用在电网、太阳能/风电逆变器、高铁等应用上。但由于成本太高以及良率问题,我们认为SiC大规模商用化的时间点会比GaN晚。

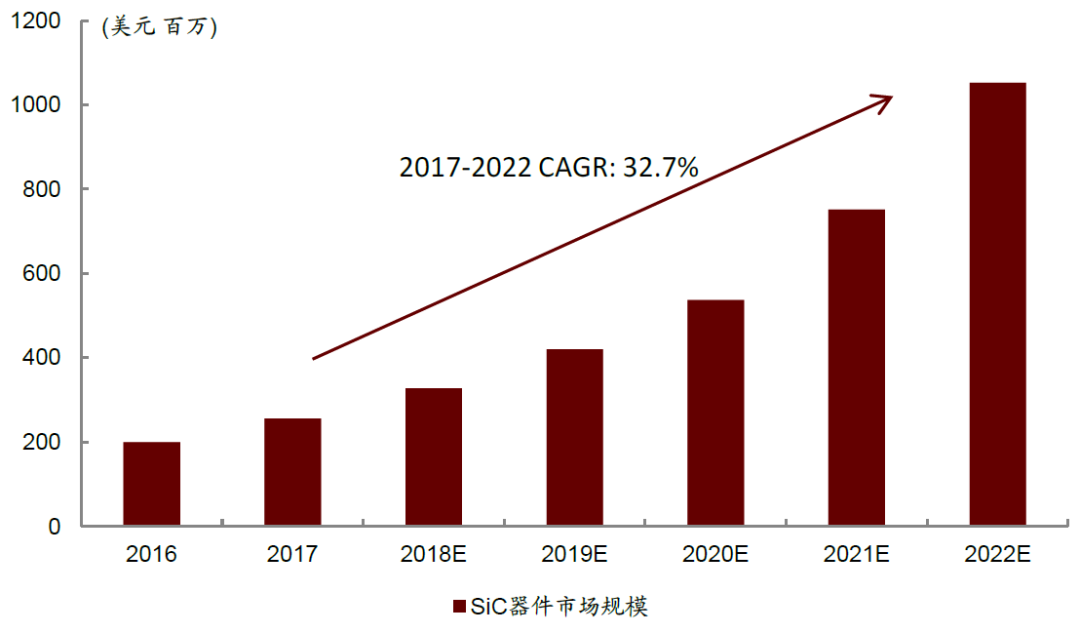

图表:SiC器件市场2017-2022 CAGR为32.7%,但值得注意的是,2020后市场规模增速变快

资料来源:Yole,中金公司研究部

注:此数据于2017年预测

(文章来源:中金点睛)